1. What are set up time and hold time constraints?

Answer

2. Give a circuit to divide frequency of clock cycle by two.

Answer

3. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

4. Explain different types of adder circuits.

Answer

5. Give two ways of converting a two input NAND gate to an inverter.

Answer

6. Draw a Transmission Gate-based D-Latch.

Answer

7. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

8. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

9. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

10. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

Answer

2. Give a circuit to divide frequency of clock cycle by two.

Answer

3. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

4. Explain different types of adder circuits.

Answer

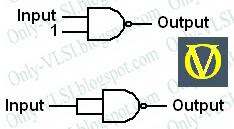

5. Give two ways of converting a two input NAND gate to an inverter.

Answer

6. Draw a Transmission Gate-based D-Latch.

Answer

7. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

8. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

9. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

10. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

Comments