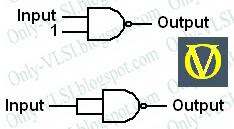

1. How do you convert a XOR gate into a buffer and a inverter (Use only one XOR gate for each)?

Answer

2. Implement an 2-input AND gate using a 2x1 mux.

Answer

3. What is a multiplexer?

Answer

4. What is a ring counter?

Answer

5. Compare and Contrast Synchronous and Asynchronous reset.

Answer

6. What is a Johnson counter?

Answer

7. An assembly line has 3 fail safe sensors and one emergency shutdown switch.The line should keep moving unless any of the following conditions arise:

(1) If the emergency switch is pressed

(2) If the senor1 and sensor2 are activated at the same time.

(3) If sensor 2 and sensor3 are activated at the same time.

(4) If all the sensors are activated at the same time

Suppose a combinational circuit for above case is to be implemented only with NAND Gates. How many minimum number of 2 input NAND gates are required?

Answer

8. In a 4-bit Johnson counter How many unused states are present?

Answer

9. Design a 3 input NAND gate using minimum number of 2 input NAND gates.

Answer

10. How can you convert a JK flip-flop to a D flip-flop?

Answer

11. What are the differences between a flip-flop and a latch?

Answer

12. What is the difference between Mealy and Moore FSM?

Answer

13. What are various types of state encoding techniques? Explain them.

Answer

14. Define Clock Skew , Negative Clock Skew, Positive Clock Skew.

Answer

15. Give the transistor level circuit of a CMOS NAND gate.

Answer

16. Design a 4-bit comparator circuit.

Answer

17. Design a Transmission Gate based XOR. Now, how do you convert it to XNOR (without inverting the output)?

Answer

18. Define Metastability.

Answer

19. Compare and contrast between 1's complement and 2's complement notation.

Answer

20. Give the transistor level circuit of CMOS, nMOS, pMOS, and TTL inverter gate.

Answer

21. What are set up time and hold time constraints?

Answer

22. Give a circuit to divide frequency of clock cycle by two.

Answer

23. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

24. Explain different types of adder circuits.

Answer

25. Give two ways of converting a two input NAND gate to an inverter.

Answer

26. Draw a Transmission Gate-based D-Latch.

Answer

27. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

28. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

29. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

30. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

31. Design 2 input AND, OR, and EXOR gates using 2 input NAND gate.

Answer

32. Design a circuit which doubles the frequency of a given input clock signal.

Answer

33. Implement a D-latch using 2x1 multiplexer(s).

Answer

34. Give the excitation table of a JK flip-flop.

Answer

35. Give the Binary, Hexadecimal, BCD, and Excess-3 code for decimal 14.

Answer

36. What is race condition?

Answer

37. Give 1's and 2's complement of 19.

Answer

38. Design a 3:6 decoder.

Answer

39. If A*B=C and C*A=B then, what is the Boolean operator * ?

Answer

40. Design a 3 bit Gray Counter.

Answer

41. Expand the following: PLA, PAL, CPLD, FPGA.

Answer

42. Implement the functions: X = A'BC + ABC + A'B'C' and Y = ABC + AB'C using a PLA.

Answer

43. What are PLA and PAL? Give the differences between them.

Answer

44. What is LUT?

Answer

45. What is the significance of FPGAs in modern day electronics? (Applications of FPGA.)

Answer

46. What are the differences between CPLD and FPGA.

Answer

47. Compare and contrast FPGA and ASIC digital designing.

Answer

48. Give True or False.

(a) CPLD consumes less power per gate when compared to FPGA.

(b) CPLD has more complexity than FPGA

(c) FPGA design is slower than corresponding ASIC design.

(d) FPGA can be used to verify the design before making a ASIC.

(e) PALs have programmable OR plane.

(f) FPGA designs are cheaper than corresponding ASIC, irrespective of design complexity.

Answer

49. Arrange the following in the increasing order of their complexity: FPGA,PLA,CPLD,PAL.

Answer

50. Give the FPGA digital design cycle.

Answer

51. What is DeMorgan's theorem?

Answer

52. F'(A, B, C, D) = C'D + ABC' + ABCD + D. Express F in Product of Sum form.

Answer

53. How many squares/cells will be present in the k-map of F(A, B, C)?

Answer

54. Simplify F(A, B, C, D) = S ( 0, 1, 4, 5, 7, 8, 9, 12, 13)

Answer

55. Simplify F(A, B, C) = S (0, 2, 4, 5, 6) into Product of Sums.

Answer

56. The simplified expression obtained by using k-map method is unique. True or False. Explain your answer.

Answer

57. Give the characteristic tables of RS, JK, D and T flip-flops.

Answer

58. Give excitation tables of RS, JK, D and T flip-flops.

Answer

59. Design a BCD counter with JK flip-flops

Answer

60. Design a counter with the following binary sequence 0, 1, 9, 3, 2, 8, 4 and repeat. Use T flip-flops.

Answer

Answer

2. Implement an 2-input AND gate using a 2x1 mux.

Answer

3. What is a multiplexer?

Answer

4. What is a ring counter?

Answer

5. Compare and Contrast Synchronous and Asynchronous reset.

Answer

6. What is a Johnson counter?

Answer

7. An assembly line has 3 fail safe sensors and one emergency shutdown switch.The line should keep moving unless any of the following conditions arise:

(1) If the emergency switch is pressed

(2) If the senor1 and sensor2 are activated at the same time.

(3) If sensor 2 and sensor3 are activated at the same time.

(4) If all the sensors are activated at the same time

Suppose a combinational circuit for above case is to be implemented only with NAND Gates. How many minimum number of 2 input NAND gates are required?

Answer

8. In a 4-bit Johnson counter How many unused states are present?

Answer

9. Design a 3 input NAND gate using minimum number of 2 input NAND gates.

Answer

10. How can you convert a JK flip-flop to a D flip-flop?

Answer

11. What are the differences between a flip-flop and a latch?

Answer

12. What is the difference between Mealy and Moore FSM?

Answer

13. What are various types of state encoding techniques? Explain them.

Answer

14. Define Clock Skew , Negative Clock Skew, Positive Clock Skew.

Answer

15. Give the transistor level circuit of a CMOS NAND gate.

Answer

16. Design a 4-bit comparator circuit.

Answer

17. Design a Transmission Gate based XOR. Now, how do you convert it to XNOR (without inverting the output)?

Answer

18. Define Metastability.

Answer

19. Compare and contrast between 1's complement and 2's complement notation.

Answer

20. Give the transistor level circuit of CMOS, nMOS, pMOS, and TTL inverter gate.

Answer

21. What are set up time and hold time constraints?

Answer

22. Give a circuit to divide frequency of clock cycle by two.

Answer

23. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

24. Explain different types of adder circuits.

Answer

25. Give two ways of converting a two input NAND gate to an inverter.

Answer

26. Draw a Transmission Gate-based D-Latch.

Answer

27. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

28. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

29. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

30. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

31. Design 2 input AND, OR, and EXOR gates using 2 input NAND gate.

Answer

32. Design a circuit which doubles the frequency of a given input clock signal.

Answer

33. Implement a D-latch using 2x1 multiplexer(s).

Answer

34. Give the excitation table of a JK flip-flop.

Answer

35. Give the Binary, Hexadecimal, BCD, and Excess-3 code for decimal 14.

Answer

36. What is race condition?

Answer

37. Give 1's and 2's complement of 19.

Answer

38. Design a 3:6 decoder.

Answer

39. If A*B=C and C*A=B then, what is the Boolean operator * ?

Answer

40. Design a 3 bit Gray Counter.

Answer

41. Expand the following: PLA, PAL, CPLD, FPGA.

Answer

42. Implement the functions: X = A'BC + ABC + A'B'C' and Y = ABC + AB'C using a PLA.

Answer

43. What are PLA and PAL? Give the differences between them.

Answer

44. What is LUT?

Answer

45. What is the significance of FPGAs in modern day electronics? (Applications of FPGA.)

Answer

46. What are the differences between CPLD and FPGA.

Answer

47. Compare and contrast FPGA and ASIC digital designing.

Answer

48. Give True or False.

(a) CPLD consumes less power per gate when compared to FPGA.

(b) CPLD has more complexity than FPGA

(c) FPGA design is slower than corresponding ASIC design.

(d) FPGA can be used to verify the design before making a ASIC.

(e) PALs have programmable OR plane.

(f) FPGA designs are cheaper than corresponding ASIC, irrespective of design complexity.

Answer

49. Arrange the following in the increasing order of their complexity: FPGA,PLA,CPLD,PAL.

Answer

50. Give the FPGA digital design cycle.

Answer

51. What is DeMorgan's theorem?

Answer

52. F'(A, B, C, D) = C'D + ABC' + ABCD + D. Express F in Product of Sum form.

Answer

53. How many squares/cells will be present in the k-map of F(A, B, C)?

Answer

54. Simplify F(A, B, C, D) = S ( 0, 1, 4, 5, 7, 8, 9, 12, 13)

Answer

55. Simplify F(A, B, C) = S (0, 2, 4, 5, 6) into Product of Sums.

Answer

56. The simplified expression obtained by using k-map method is unique. True or False. Explain your answer.

Answer

57. Give the characteristic tables of RS, JK, D and T flip-flops.

Answer

58. Give excitation tables of RS, JK, D and T flip-flops.

Answer

59. Design a BCD counter with JK flip-flops

Answer

60. Design a counter with the following binary sequence 0, 1, 9, 3, 2, 8, 4 and repeat. Use T flip-flops.

Answer

Comments

Home Shifting & Packing Service Islamabad

virginia bankruptcy means test

bankrupty lawyer near me

Codeme Hub- Best Data Analytics course in Kerala.

https://codemehub.com/best-data-analytics-course-in-calicut-kerala/

artificial intelligence training in Pune

septic tank cleaning services in tirunelveli

Embedded training center in Chennai

best embedded training institute in Chennai

plc training center in Chennai

plc scada vfd dcs hmi training institute in Chennai

best plc training institute n Chennai

best final year project center in chennai

best embedded training institute in Chennai

plc training center in Chennai

plc scada vfd dcs hmi training institute in Chennai

best final year Project center in Chennai

best final year Project center in Chennai

Wooden Manai Palagai 10*16*5

Garuda Puran Hindi Book

sivapuranam tamil book

ramayanam book

sarva muhurtha panchangam

check it out - Loan Origination Software

Keep up the excellent work

Sharepoint Training from Hyderabad

Best Servicenow Training from Hyderabad

MSBI Online Training from India

JAVA Full Stack Online Training from Chennai

Best MongoDB Training Institute In India