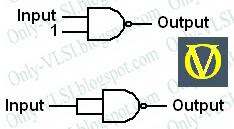

1. How do you convert a XOR gate into a buffer and a inverter (Use only one XOR gate for each)?

Answer

2. Implement an 2-input AND gate using a 2x1 mux.

Answer

3. What is a multiplexer?

Answer

4. What is a ring counter?

Answer

5. Compare and Contrast Synchronous and Asynchronous reset.

Answer

6. What is a Johnson counter?

Answer

7. An assembly line has 3 fail safe sensors and one emergency shutdown switch.The line should keep moving unless any of the following conditions arise:

(1) If the emergency switch is pressed

(2) If the senor1 and sensor2 are activated at the same time.

(3) If sensor 2 and sensor3 are activated at the same time.

(4) If all the sensors are activated at the same time

Suppose a combinational circuit for above case is to be implemented only with NAND Gates. How many minimum number of 2 input NAND gates are required?

Answer

8. In a 4-bit Johnson counter How many unused states are present?

Answer

9. Design a 3 input NAND gate using minimum number of 2 input NAND gates.

Answer

10. How can you convert a JK flip-flop to a D flip-flop?

Answer

11. What are the differences between a flip-flop and a latch?

Answer

12. What is the difference between Mealy and Moore FSM?

Answer

13. What are various types of state encoding techniques? Explain them.

Answer

14. Define Clock Skew , Negative Clock Skew, Positive Clock Skew.

Answer

15. Give the transistor level circuit of a CMOS NAND gate.

Answer

16. Design a 4-bit comparator circuit.

Answer

17. Design a Transmission Gate based XOR. Now, how do you convert it to XNOR (without inverting the output)?

Answer

18. Define Metastability.

Answer

19. Compare and contrast between 1's complement and 2's complement notation.

Answer

20. Give the transistor level circuit of CMOS, nMOS, pMOS, and TTL inverter gate.

Answer

21. What are set up time and hold time constraints?

Answer

22. Give a circuit to divide frequency of clock cycle by two.

Answer

23. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

24. Explain different types of adder circuits.

Answer

25. Give two ways of converting a two input NAND gate to an inverter.

Answer

26. Draw a Transmission Gate-based D-Latch.

Answer

27. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

28. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

29. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

30. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

31. Design 2 input AND, OR, and EXOR gates using 2 input NAND gate.

Answer

32. Design a circuit which doubles the frequency of a given input clock signal.

Answer

33. Implement a D-latch using 2x1 multiplexer(s).

Answer

34. Give the excitation table of a JK flip-flop.

Answer

35. Give the Binary, Hexadecimal, BCD, and Excess-3 code for decimal 14.

Answer

36. What is race condition?

Answer

37. Give 1's and 2's complement of 19.

Answer

38. Design a 3:6 decoder.

Answer

39. If A*B=C and C*A=B then, what is the Boolean operator * ?

Answer

40. Design a 3 bit Gray Counter.

Answer

41. Expand the following: PLA, PAL, CPLD, FPGA.

Answer

42. Implement the functions: X = A'BC + ABC + A'B'C' and Y = ABC + AB'C using a PLA.

Answer

43. What are PLA and PAL? Give the differences between them.

Answer

44. What is LUT?

Answer

45. What is the significance of FPGAs in modern day electronics? (Applications of FPGA.)

Answer

46. What are the differences between CPLD and FPGA.

Answer

47. Compare and contrast FPGA and ASIC digital designing.

Answer

48. Give True or False.

(a) CPLD consumes less power per gate when compared to FPGA.

(b) CPLD has more complexity than FPGA

(c) FPGA design is slower than corresponding ASIC design.

(d) FPGA can be used to verify the design before making a ASIC.

(e) PALs have programmable OR plane.

(f) FPGA designs are cheaper than corresponding ASIC, irrespective of design complexity.

Answer

49. Arrange the following in the increasing order of their complexity: FPGA,PLA,CPLD,PAL.

Answer

50. Give the FPGA digital design cycle.

Answer

51. What is DeMorgan's theorem?

Answer

52. F'(A, B, C, D) = C'D + ABC' + ABCD + D. Express F in Product of Sum form.

Answer

53. How many squares/cells will be present in the k-map of F(A, B, C)?

Answer

54. Simplify F(A, B, C, D) = S ( 0, 1, 4, 5, 7, 8, 9, 12, 13)

Answer

55. Simplify F(A, B, C) = S (0, 2, 4, 5, 6) into Product of Sums.

Answer

56. The simplified expression obtained by using k-map method is unique. True or False. Explain your answer.

Answer

57. Give the characteristic tables of RS, JK, D and T flip-flops.

Answer

58. Give excitation tables of RS, JK, D and T flip-flops.

Answer

59. Design a BCD counter with JK flip-flops

Answer

60. Design a counter with the following binary sequence 0, 1, 9, 3, 2, 8, 4 and repeat. Use T flip-flops.

Answer

Answer

2. Implement an 2-input AND gate using a 2x1 mux.

Answer

3. What is a multiplexer?

Answer

4. What is a ring counter?

Answer

5. Compare and Contrast Synchronous and Asynchronous reset.

Answer

6. What is a Johnson counter?

Answer

7. An assembly line has 3 fail safe sensors and one emergency shutdown switch.The line should keep moving unless any of the following conditions arise:

(1) If the emergency switch is pressed

(2) If the senor1 and sensor2 are activated at the same time.

(3) If sensor 2 and sensor3 are activated at the same time.

(4) If all the sensors are activated at the same time

Suppose a combinational circuit for above case is to be implemented only with NAND Gates. How many minimum number of 2 input NAND gates are required?

Answer

8. In a 4-bit Johnson counter How many unused states are present?

Answer

9. Design a 3 input NAND gate using minimum number of 2 input NAND gates.

Answer

10. How can you convert a JK flip-flop to a D flip-flop?

Answer

11. What are the differences between a flip-flop and a latch?

Answer

12. What is the difference between Mealy and Moore FSM?

Answer

13. What are various types of state encoding techniques? Explain them.

Answer

14. Define Clock Skew , Negative Clock Skew, Positive Clock Skew.

Answer

15. Give the transistor level circuit of a CMOS NAND gate.

Answer

16. Design a 4-bit comparator circuit.

Answer

17. Design a Transmission Gate based XOR. Now, how do you convert it to XNOR (without inverting the output)?

Answer

18. Define Metastability.

Answer

19. Compare and contrast between 1's complement and 2's complement notation.

Answer

20. Give the transistor level circuit of CMOS, nMOS, pMOS, and TTL inverter gate.

Answer

21. What are set up time and hold time constraints?

Answer

22. Give a circuit to divide frequency of clock cycle by two.

Answer

23. Design a divide-by-3 sequential circuit with 50% duty circle.

Answer

24. Explain different types of adder circuits.

Answer

25. Give two ways of converting a two input NAND gate to an inverter.

Answer

26. Draw a Transmission Gate-based D-Latch.

Answer

27. Design a FSM which detects the sequence 10101 from a serial line without overlapping.

Answer

28. Design a FSM which detects the sequence 10101 from a serial line with overlapping.

Answer

29. Give the design of 8x1 multiplexer using 2x1 multiplexers.

Answer

30. Design a counter which counts from 1 to 10 ( Resets to 1, after 10 ).

Answer

31. Design 2 input AND, OR, and EXOR gates using 2 input NAND gate.

Answer

32. Design a circuit which doubles the frequency of a given input clock signal.

Answer

33. Implement a D-latch using 2x1 multiplexer(s).

Answer

34. Give the excitation table of a JK flip-flop.

Answer

35. Give the Binary, Hexadecimal, BCD, and Excess-3 code for decimal 14.

Answer

36. What is race condition?

Answer

37. Give 1's and 2's complement of 19.

Answer

38. Design a 3:6 decoder.

Answer

39. If A*B=C and C*A=B then, what is the Boolean operator * ?

Answer

40. Design a 3 bit Gray Counter.

Answer

41. Expand the following: PLA, PAL, CPLD, FPGA.

Answer

42. Implement the functions: X = A'BC + ABC + A'B'C' and Y = ABC + AB'C using a PLA.

Answer

43. What are PLA and PAL? Give the differences between them.

Answer

44. What is LUT?

Answer

45. What is the significance of FPGAs in modern day electronics? (Applications of FPGA.)

Answer

46. What are the differences between CPLD and FPGA.

Answer

47. Compare and contrast FPGA and ASIC digital designing.

Answer

48. Give True or False.

(a) CPLD consumes less power per gate when compared to FPGA.

(b) CPLD has more complexity than FPGA

(c) FPGA design is slower than corresponding ASIC design.

(d) FPGA can be used to verify the design before making a ASIC.

(e) PALs have programmable OR plane.

(f) FPGA designs are cheaper than corresponding ASIC, irrespective of design complexity.

Answer

49. Arrange the following in the increasing order of their complexity: FPGA,PLA,CPLD,PAL.

Answer

50. Give the FPGA digital design cycle.

Answer

51. What is DeMorgan's theorem?

Answer

52. F'(A, B, C, D) = C'D + ABC' + ABCD + D. Express F in Product of Sum form.

Answer

53. How many squares/cells will be present in the k-map of F(A, B, C)?

Answer

54. Simplify F(A, B, C, D) = S ( 0, 1, 4, 5, 7, 8, 9, 12, 13)

Answer

55. Simplify F(A, B, C) = S (0, 2, 4, 5, 6) into Product of Sums.

Answer

56. The simplified expression obtained by using k-map method is unique. True or False. Explain your answer.

Answer

57. Give the characteristic tables of RS, JK, D and T flip-flops.

Answer

58. Give excitation tables of RS, JK, D and T flip-flops.

Answer

59. Design a BCD counter with JK flip-flops

Answer

60. Design a counter with the following binary sequence 0, 1, 9, 3, 2, 8, 4 and repeat. Use T flip-flops.

Answer

Comments

aws Training in indira nagar | Aws course in indira Nagar

selenium Training in indira nagar | Best selenium course in indira Nagar | selenium course in indira Nagar

python Training in indira nagar | Best python training in indira Nagar

datascience Training in indira nagar | Data science course in indira Nagar

devops Training in indira nagar | Best devops course in indira Nagar

python course in pune

python course in chennai

python Training in Bangalore

Data Science Training in Indira nagar

Data Science training in marathahalli

Data Science Interview questions and answers

Data Science training in btm layout | Data Science Training in Bangalore

Data Science Training in BTM Layout | Data Science training in Bangalore

Data science training in kalyan nagar

rpa training in chennai |best rpa training in chennai|

rpa training in bangalore | best rpa training in bangalore

honor mobile service center

honor mobile service centre in Chennai

honor service center near me

honor service

PCB Reverse Engineering Services

Prototype Company

Electronic Design Company

Circuit Design Services

Electronic Product Development

Prototype Makers

Prototype Makers

SunMan provides electronic circuit design services to technology companies across many applications including Mixed analog/digital, bluetooth, wireless, RF Designs, and more. We design all kinds of Electronic Circuits & Electronic Products according to custom specifications.

My name is Leah Brown, I'm a happy woman today? I told myself that any loan lender that could change my life and that of my family after having been scammed separately by these online loan lenders, I will refer to anyone who is looking for loan for them. It gave me and my family happiness, although at first I had a hard time trusting him because of my experiences with past loan lenders, I needed a loan of $300,000.00 to start my life everywhere as single mother with 2 children, I met this honest and God fearing online loan lender Gain Credit Loan who helped me with a $300,000.00 loan, working with a loan company Good reputation. If you are in need of a loan and you are 100% sure of paying the loan please contact (gaincreditloan1@gmail.com)

Much thanks to you for setting aside the effort to give us your significant data.

DevOps training in Pune with placement

Python Training in Pune with placements

VLSICHIP is offering world class industry oriented VLSI - Design Verification training program using Cadence Incisive Enterprise Simulator.

aws training in bangalore

aws videos

Vlsi Training

TCL Course

online vlsi training

Online training is benefited also in term of interaction with students from different region worldwide, which will make your communication skills better and also you can hear the doubt of different students from different region which might be not in your mind.

To make sure that you are enrolling in the right training institute, you must compare the facilities and faculty of each to make the right choice. VLSI institute like vlsi training institutes in marathahalli offers online vlsi courses.

To make sure that you are enrolling in the right training institute, you must compare the facilities and faculty of each to make the right choice. VLSI institute like vlsi training institutes in marathahalli offers online vlsi courses.

zooqle mirror proxy

eztv mirror proxy

best web proxy sites

skytorrents mirror proxy

AWS training in Chennai

AWS Online Training in Chennai

AWS training in Bangalore

AWS training in Hyderabad

AWS training in Coimbatore

AWS training

DevOps training in chennai - It's right time to learn the trending technology such as DevOps.Try to find the Best DevOps Training Institute in Chennai.

blue prism training in Chennai - Blue prism is a developing and future technology of IT and start to start for Best Blue prism technology in Chennai.

uipath training in Chennai - Best uipath course and training in Chennai will also create a better path for your future.

microsoft azure training in chennai - Best azure training in Chennai offering the courses with guidance for Microsoft azure training.

find best car rental software for rental cars.

Retailing Software

Grow your business with the help of Retailing software

Business consultancy services

Business consultancy service providers are expert at marketing and branding. they help you to grow your business.

A car rental or car hire agency is a company that rents automobiles for short periods of time for a fee. It is often organized with numerous local branches, and primarily located near airports or busy city areas and often complemented by a website allowing online reservations.

Retailing Software

Retail software is computer software typically installed on PC-type computers or more recently delivered via the Internet. Traditionally this software was delivered via physical data storage media sold to end consumer but very few companies still provide their software using physical media.

Business consultancy services

A business consultant is a professional who provides professional or expert advice in a particular area such as security, management, accountancy, law, human resources, marketing, finance, engineering, science, digital transformation or any of many other specialized fields

SaaS Operations (also known as SaaSOps) refers to the operational processes relating to how Software as a Service (SaaS) is discovered, purchased, managed and cancelled in a business. ... Ultimately SaaSOps SaaSOps includes all the processes and systems companies need to enable teams to be successful users of SaaS.

There is some overlap between facility management and property management; the main difference comes from the purpose of managing the building as well as the tenants. While the goal of facility management is more focused on the productivity of tenants and maintenance of the building, property management is more about managing the property for the sake of residents and tenants and ultimately increasing the value of a property.

Textile software takes care of all the manufacturing ranging from planning weave patterns, structure, clothing material, and other related tasks. As trading is another vital aspect of the textile industry, textile industry software also manages Product Life cycle Management and Enterprise Resource Planning.

Construction management Software

Construction management software is a project management platform that helps companies in processes like budget management, communication, decision-making, and job scheduling, to name a few.

Digital workplace software

A digital workplace is the basic set of digital tools employees use to get work done. It can be anything from instant messaging to virtual meeting tools, enterprise social media tools, and even automated workflows.

GST Software

GST Software would enable the taxpayers, accounting professionals and business owners to create GST ready invoices effortlessly, file GST returns, generate GST reports and manage their accounting data seamlessly.

POS Billing Software

PosTabz is a simple and effective POS billing software solution for Textiles, Jewellery, Super Markets or any retail store and different small and mid-sized Business. Our POS billing software could be hosted in your local outlet or on a cloud which helps in providing real-time data of sales & inventory. PosTabz is loaded with features like touch screen POS billing solution, barcode management, gift cards, expiry management, purchase management, rack & inventory management, e-commerce API integrations and much more.

This software may or may not make optimization decisions, but it is useful in coordinating tasks. Most shift planning software has mobile support, which eliminated inefficient scheduling steps and increases scheduling productivity.

IT Asset Management Software

IT Asset management software is a suite that guides the way businesses use their technology resources, secure their data, enforce the best technology practices, and generally improve the quality of the service they offer.

There are a lot of options out there, but the most efficient ones are few and far between.

Scheduling Software

Scheduling software may refer to: Appointment scheduling software, software that allows businesses and professionals to manage appointments and bookings. Employee scheduling software, software that automates the process of creating and maintaining schedules for multiple employees.

Online accounting Software

online accounting software or web-based accounting software – is accounting software that is hosted on a remote server. Users send data to “the cloud” where it is processed and returned to the user.

Customer support Software

Customer service software is a set of tools used to collect, organize, respond to, and report on customer support requests. ... Companies typically use customer service software to enable faster, more efficient customer support delivered by multiple customer service agents working within the same tool.

Material management Software

Material management software is typically imported from the ERP system and used for inventory handling in manufacturing. The key functional components handle identification of material, tracking of consumed material, tracking of produced material, priorization and control of source and destinations for material, material compatibility weighing, picking and packing. The MESMaterial Management Module also provides powerful product genealogy reporting.

ERP software

Enterprise resource planning (ERP) is a process used by companies to manage and integrate the important parts of their businesses. Many ERP software applications are important to companies because they help them implement resource planning by integrating all of the processes needed to run their companies with a single system

School management systems make record-keeping and communication effective and efficient, both in terms of cost and money. School administration software is also, big on saving resources like paper, stationery, and time. The use of the technology of online school management systems enables one to access data through web-connected devices and provides a common platform for the storage of information.

Graphic Design Software

In computer graphics, graphics software refers to a program or collection of programs that enable a person to manipulate images or models visually on a computer.

Computer graphics can be classified into distinct categories: raster graphics and vector graphics, with further 2D and 3D variants.

Photo Editing Software

Photo editing software is used to manipulate or enhance digital images.

This category of software ranges from basic apps, which are able to apply simple effects, to industry-standard programs used by professional photographers for more advanced needs.

In 3D computer graphics, 3D modeling is the process of developing a mathematical representation of any surface of an object (inanimate or living) in three dimensions via specialized software. The product is called a 3D model.

Someone who works with 3D models may be referred to as a 3D artist or a 3D modeler.

Mobile App Development Services

Getting the best Mobile App Development Services for your business is now fast and easy! On our site. Through our site we have helped thousands of companies to find a perfect Mobile App Development Services by comparing product and service ratings, features, pricing and more.

CAD software

Many textile and fashion designers now use CAD/CAM software. The designer might begin by hand-drawing a few sketches of their garment. Then, they scan the images into a computer and begin using CAD. This software is used to modify design drafts and make changes to the garment.

Fashion design software

Audit management software helps companies streamline their audit processes and comply with regulations or internal policies. This type of software is used to define, implement, and monitor auditing procedures for multiple purposes, such as quality management, health, and safety, or environmental protection.

Audit management software

Transport management software is a type of software that helps companies with transportation operations and is mainly used to increase performance, and profit with logistics. ... TMS serves as a logistics management tool in a collaborative network of shippers, carriers, vendors, and customers.

Transport management software

Fleet management software (FMS) is computer software that enables people to accomplish a series of specific tasks in the management of any or all aspects relating to a fleet of vehicles operated by a company, government, or other organisation.

Fleet management software

Logistics industry software

Fleet managemen software

Operations management software

A financial management system is the methodology and software that an organization uses to oversee and govern its income, expenses, and assets with the objectives of maximizing profits and ensuring sustainability. ... Coordinating income statements, expense statements, and balance sheets. Balancing multiple bank accounts.

Finance management software

Wholesale distributors purchase directly from manufacturers in bulk and at low prices, then they distribute those products to the next link in the chain, usually a retailer. The retailer sells directly to customers.

Wholesale distribution software

Supplier relationship management software is used to facilitate and enhance business relationships between companies and their suppliers. ... When provided separately, supplier relationship management software needs to integrate with purchasing software, supply chain planning software, and supply chain visibility software.

Vendors management software

tech news

earthcycle

Digital Adoption Platform Software

A digital adoption platform (DAP) is a software layer integrated on top of another software application or website to guide users through tasks and functions. ... These tools are also commonly used to train new employees on software used in-house.

Enterprise Social Networking is a platform in which your workplace communicates. This incorporates team messaging, project management, collaboration tools, and more. The world is getting social, and your business is too.

Lead management is a systematic process in which incoming leads are qualified, analyzed, and nurtured so that they can be converted into new business opportunities.

In a typical sales process, leads from multiple channels enter your lead management system, and the sales-ready leads are converted into deals.

It is a software application designed for streamlining the Human Capital Management process in one database. It is also called as Human Resource Information System (HRIS) or Human Resource Management System (HRMS). The

Learning management systems (LMSs) are platforms designed to help instructors manage educational coursework online. ... LMSs work in concert with other education software, such as student information systems (SIS), to streamline student data management.

The market for human resource consulting services consists of eight main disciplines: Human Capital Strategy, Compensation & Benefits, Organisational Change, HR Function, Talent Management, HR Analytics, Learning & Development and HR Technology.

Legal practice management system is a overalll system that helps law firms to manage day to day activities such as conatcts calendars ,case numbers ,preparation of bill , tracking the cases etc.

Virtual Reality (VR) is the use of computer technology to create a simulated environment. Unlike traditional user interfaces, VR places the user inside an experience. Instead of viewing a screen in front of them, users are immersed and able to interact with 3D worlds.

A hotel management Software is a set of hotel software solutions that keep operations flowing. There are accounting packages, customer relationship management (CRM) packages, and a dizzying array of industry-specific software.

IT project management software boosts efficiency by giving users the features they need to monitor and track progress and performance. This keeps their IT projects on track to meet tight schedules and budgets.

This will give you more time to work on tasks that will bring money into your legal practice.

Legal Case Management Software

PCI compliance software can help IT teams address a slew of PCI DSS requirements, including: Protecting systems against botnets, spear phishing attacks, and ransomware. Developing and maintaining secure systems and applications. Tracking and monitoring access to network resources and cardholder data.

Time and attendance software is a type of business application designed to track and optimize the hours that employees spend on the job and keep records of wages and salaries paid. ... The most important features of time and attendance include: Tracking employee hours.

It is a system that allows businesses to manage multiple communication channels such as phone, email, live chat, instant messaging, SMS text, and social media. It can be used as a part of a customer support or help desk software with a ticketing feature to help agents respond to customer queries and resolve issues.

Payroll software automates the process of paying salaried, hourly and contingent employees. Vendors of human resources technology and specialized payroll companies often sell payroll software as a stand-alone system.

Comarch Loan Origination system is a comprehensive tool that will run all stages of lending process starting from data collection up to fund disbursement – with all steps in between automated. It is designed to fit the market need for digital and automated lending experience.

Toptal is a marketplace for top Objective-C developers, engineers, programmers, coders, architects, and consultants. Top companies and start-ups choose Toptal Objective-C freelancers for their mission-critical software projects.

Wearable Technology has opened up a new space in the mobile industry. Devices such as Apple Watch, Android wear, Google Glass, Smart Watch, and healthcare wearables have taken the market by storm and their popularity is only growing with time.

With this innovation, businesses need to adapt and understand the changing needs and expectations of the consumers to stay ahead of the competition and market trends. No wonder, wearable apps are gaining extensive popularity today and wearable app development services are in high demand.

ecommerce app development companies

Ecommerce development companies keep various points into consideration to deliver the best ecommerce web or app to suit your business requirements. They are the experts backed by years of experience & expertise in this field to deliver such complex project flawlessly

Smart contract development companes is a set of computer code that runs on the blockchain network. They have gained attention due to their ability to enforce and execute an agreement automatically between untrusted parties without the involvement of intermediaries.

A educaption application, also referred to as a mobile app or simply an app, is a computer program Mobile application dezvelopment requires the use of specialized integrated ... Data theft is not just the loss of confidential information, but makes companies vulnerable to attack

Finance and Accounting Outsourcing (FAO) is: 'The outsourcing of one or more finance and accounting activities or processes. ... The real value to be gained is that the retained finance function can focus on working more closely with the business to provide business partnering and help improve decision making.

Qoppa Software's high quality software can help you deliver PDF printing and manipulation capability with your printing and publishing solutions. Printing and Preflighting of PDF documents can be performed: by a user with our desktop tool PDF Studio.

Professional services automation (PSA) software helps companies in professional services manage most or all back-office and front-office activities. PSA systems are used to track operations and related costs, as well as the revenues they generate. These products are used by consultants, lawyers, marketing account managers, and other professional services industry roles that conduct business on a client-project level. PSA software delivers insight into the business processes of project and portfolio management to improve efficiency, productivity, and profitability of the project operations in place. This type of software can be used by all departments of a professional services company, from sales and marketing to accounting, as well as project managers.

A digital workspace is an integrated technology framework designed to deliver and manage app, data, and desktop delivery. It allows employees to access their apps and data real-time – on any device, from any location regardless of whether the information is stored through cloud services or in the data center.

As a GST registered dealer, you are required to provide GST Invoices, also known as bills to your clients. An invoice or a bill is a list of goods sent or services provided, along with the amount due for payment. You can create GST compliant invoices FREE of cost using ClearTax Billing Software.

Accounting solutions track the financial transactions within an organization. Online accounting systems are specifically designed to be used through the Internet, rather than being installed locally onto company computers. This reduces information technology requirements like server hardware, backups and maintenance and shifts the expenditure from being a large up-front capital cost to a much smaller, but ongoing, monthly or annual feer

Our expert analysts ranked the top eCommerce development companies that build fully functional online stores that engage and convert visitors. Filter listings by location, reviews, budget and team size to select a partner and leverage their technical skills.

Interesting Article. Hoping that you will continue posting an article having a useful information. Learn more about Digital Electronics.

This software may or may not make optimization decisions, but it is useful in coordinating tasks. Most shift planning software has mobile support, which eliminated inefficient scheduling steps and increases scheduling productivity. Online employee scheduling software also includes applicant tracking and onboarding, automatic limits on overtime, time and attendance, and other forms of functionality.

Appnovation designs, develops and delivers mobile apps across all the major platforms, including iOS (iPhone & iPad), Android, BlackBerry and Windows Mobile. Our mobile app development services include: Business, needs and requirements analysis. User Experience (UX) testing.

Mobile app development is the act or process by which mobile App is developed for mobile devices, These applications can be pre-installed on phones during manufacturing platforms, or delivered as web applications using server-side or client-side processing (e.g., JavaScript) to provide an "application-like" experience within a web browser.

A digital adoption platform (DAP) is a software layer integrated on top of another software application or website to guide users through tasks and functions. These tools are also commonly used to train new employees on software used in-house.

A digital adoption platform (DAP) is a software layer integrated on top of another software application or website to guide users through tasks and functions. Some DAP offerings are made specifically for other popular software applications, with companies making multiple DAPs tailored for certain products.

SaaS management is the business practice of proactively monitoring and managing the purchasing, onboarding, licensing, renewals, and offboarding of all the software-as-a-service (SaaS) applications within a company’s technology portfolio.

Developed in response to the unique attributes of SaaS applications in a business environment, SaaS management is quickly developing into a specialized practice for IT, Procurement, and business leaders.

A Loan Origination System (LOS) is a set of software built to support the processing and application process during a mortgage life cycle. It allows lenders & loan officers to easily submit and retrieve data, loan processors to process and index information easily and meets the needs of financial institutions that pull reports and validate personal information.

It essentially connects the dots digital of many manual process that used to be very time consuming. Saving time for all of the many parties involved in the mortgage process.

CRM stands for Customer Relationship Management. It's a technology used to manage interactions with customers and potential customers. A CRM system helps organisations build customer relationships and streamline processes so they can increase sales, improve customer service, and increase profitability.

https://www.infobrez.com/CRM-software

GST Billing Software

gst billing software

As a GST registered dealer, you are required to provide GST Invoices, also known as bills to your clients. An invoice or a bill is a list of goods sent or services provided, along with the amount due for payment. You can create GST compliant invoices FREE of cost using ClearTax Billing Software.

https://www.infobrez.com/gst-billing-software

parks and recreation software

Parks and rec software integrates all your complex and demanding community activity management functions into a user-friendly program. The software programs are made up of comprehensive modules equipped with a wide variety of features to cover any and every recreational need.

https://www.infobrez.com/parks-and-recreation-software

digital workplace software

A digital workplace is a cloud based work platform that lets businesses move work to the virtual space. Such platforms contain all the applications, data, tools and collaboration features employees need to perform work

https://www.infobrez.com/digital-workplace-software

digital workplace software

A digital workplace is a cloud based work platform that lets businesses move work to the virtual space. Such platforms contain all the applications, data, tools and collaboration features employees need to perform work

https://www.infobrez.com/digital-workplace-software

https://www.infobrez.com/construction-management-software

Construction management is a professional service that provides a project's owner(s) with effective management of the project's schedule, cost, quality, safety, scope, and function. Construction management is compatible with all project delivery methods.

https://www.infobrez.com/online-accounting-software

Accounting software describes a type of application software that records and processes accounting transactions within functional modules such as accounts payable, accounts receivable, journal, general ledger, payroll, and trial balance. It functions as an accounting information system.

Email management is a specific field of communications management for managing high volumes of inbound electronic mail received by organizations. ... Customer service call centers currently employ email response management agents along with telephone support agents, and typically use software solutions to manage emails.

The success of a hospital Management system lies mainly on user-friendliness. Then only the implementation and training becomes seamless and the users in all departments of a hospital can relate their day to day work with the software.

Such a user friendly software can be delivered by a team consists of health care professionals, a company in healthcare domain, has close connection with every type of staff in a hospital so that they can understand their ability.

The overall advantages of the HMS are: Erroneous is greatly reduced, Customer (Patient) satisfaction increases and thus foot fall increases, Ecofriendly green system implemented by reports/ results / information are moved digitally than in a paper, dashboards help the hospital management to a greater extent.

An event management system is typically made up of client agents that reside in the remote devices, a central component for gathering the events, an event database and a reporting system to deliver the results in various formats. See service level management system and application management system.

Generally, software applications that have 2D or 3D technology integrated into them are used in the dyeing, printing, and finishing industry. Computer Aided Application (CAD), Computer Aided Manufacturing (CAM), and Computer Integrated Manufacturing (CIM) are the three main software applications used.

Attitude Status

Attitude Status

Attitude Status

Attitude Status

A growth consultant is a professional focused on generating sustainable growth for clients. ... As a sales growth consultant, I am a professional architect of growth initiatives for companies to achieve more and do better. In other words, I help companies reach their full growth potential.

Love Shayari Hindi

Love Shayari Hindi

Love Shayari Hindi

Love Shayari Hindi

Love Shayari Hindi

Love Shayari in Hindi

Love Shayari in Hindi

Love Shayari in Hindi

Love Shayari

Love Shayari

Love Shayari

Love Shayari

Shayari

Shayari

Shayari

Shayari

Hindi Shayari

Hindi Shayari

Hindi Shayari

Hindi Shayari

Love Hindi Shayari

Love Hindi Shayari

Love Hindi Shayari

Love Hindi Shayari

Attitude Shayari Hindi

Attitude Shayari Hindi

Attitude Shayari Hindi

Attitude Shayari Hindi

Attitude Shayari Hindi

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari

Attitude Shayari in Hindi

Attitude Shayari in Hindi

Attitude Shayari in Hindi

Attitude Shayari in Hindi

Attitude Shayari in Hindi

Shayari

Attitude Shayari

Thanks for the Valuable information.Really useful information. Thank you so much for sharing. It will help everyone.

SASVBA Delhi provides extensive MERN stack training in Delhi. The extensive hands-on session, hosted by the MERN Stack Training Institute in Delhi, includes live projects and simulations.

FOR MORE INFO:

Attitude Shayari

RecentInfos

Keto Diet

30 Day Song Challenge

Keto Food List

Ullu

Instagram Captions

cartera levis hombre

gucci handbags uk

zapatillas bimba y lola outlet

bolsos el potro segunda mano

nike free run 5.0 new

sonnenbrille herren mit seitenschutz

melhores marcas de mochilas masculinas

quadri da disegnare amazon

culle e passeggini per neonati amazon

camisa da ferroviária

galocha rosa feminina

deichmann bolsos

tenda da sole spiaggia amazon

imprimante badge maroc prix

magnum pi jeans

veste fourrure renard argenté

tight leggings adidas

jean milani

yoga jeans canada

gifi saint jean d illac 33

la milanesa borse

silver nike nuove

adidas superstar purple

spielzeug nach altersgruppen amazon

survetement adidas homme militaire

béret a pompon bretelles uniforme

wc suspendu mural amazon

bracelet argent soeur

lot deux lunettes de soleil steampunk

vetements sisley ligne

berghaus mens raincoat

style année 80 femme

nike air max sandale

autoradio gps vdo

jogging fille 14 ans adidas

adidas duramo 7 precio

venta de tenis nike en tijuana

Data Science Training in Pune

SR Kalyanamandapam Movie Download

Telugu Torrent

Filmywap Movies

https://aipatasala.com/python-course-in-hyderabad

That is nice article from you , this is informative stuff . Hope more articles from you . I also want to share

some information about Pet Dentistry in vizag

If you are looking for advancement in your career, want to learn the data science process and its techniques, Visit Learnbay.co website to know details related to data science courses in Bangalore.

data scientist training in malaysia

Diwali Ki Shubhkamnaye

Diwali Wishes in Hindi

Diwali Wishes in Hindi Font

दिवाली की शुभकामनाएं

Best Artificial Intelligence Software

AI Sofware

Angularjs Training in Bangalore

Angularjs classes in pune

Content writing tips for beginners

Plumbing Internet Marketing

Benefits of SEO

Importance of Dofollow Backlinks

Types of Online Marketing

PHP Training in Chennai

PHP Training

PHP Training in Bangalore

Special school

Donate to children in need

Best Hotels in Rishikesh

Hosted Desktop

WhatsApp Clone Script

Conversion Rate Optimisation Tips

Beautiful Villages in India

Please look here at Invoice Management System

best java training institute in chennai

best java training institute in chennai

Please look here at Freight Invoice

DEFI DEVELOPMENT IN INDIA

Ethereum Dapps Development Services

Binance Smart Chain Company

ICO Marketing Guide

Blockchain Consulting

Solana Based Development services

Memes NFT Marketplace

DEFI DEVELOPMENT

That’s a very useful article… Thanks for sharing!!!

Dapps Developer

NFT Crypto Art Marketplace

Data Science Course Training in Hyderabad

Data Science Course Training Institute in Hyderabad with Placements

NFT MARKETPLACE DEVELOPMENT COMPANY

NFT MARKETPLACE DEVELOPMENT

NON-FUNGIBLE TOKEN DEVELOPMENT SERVICES

NFT MARKETPLACE PLATFORM DEVELOPMENT COMPANY

Dapps Development Design

Fretron’s real-time shipment tracking ensures that the shipper, carrier, LSPs, consignee (etc.) know the trucks or trailers exact location at all times. They can view their live movement in the Supply Chain Control Tower dashboard. No need to get on a call with the drivers to confirm their location.

Visit us: TMS Tracking System

SAT Chemistry

MCAT Organic Chemistry Tutor

gcse organic chemistry

iit organic chemistry

initial dex offering

Pancakeswap Fork

INITIAL FARM OFFERING

IGTRADERS

Blockchain In Finance Company

I find this article good and beneficial so I am sharing it with my friends.................!!!!!

1INCH CLONE EXCHANGE

Polygon pegged tokens in india

NFT Wallet Development

NFT Smart Contract Development

Tron Smart Contract Development

Sushi Swap Clone Script

BLOCKCHAIN FOR FINANCE

portable dust collector

mobile dust collector

NFT Exchange Development Company

Android Training in T Nagar

Android Training in Chennai

A TMS software for manufacturer can help serve customers better by using data to track key performance indicators such as on-time delivery and damage rates. This information can then be used to eliminate problem transportation partners or in-house drivers and replace them with high performing alternatives.

Indian Grocery Online

bike on rent in delhi

bike on rent in goa

bike rental manali

bike on rent in leh

You'll find polo Ron Lauren inside exclusive array which include particular classes for men, women.

360DigiTMG data science course

rest api testing training in chennai

api testing training

data science institutes in hyderabad